## Тема 7. Создание микро и наноприборов

Содержание темы: [История микроэлектроники](#), [Биполярный и полевой транзисторы](#), [Примеры промышленных МОП транзисторов](#), [FinFet транзисторы](#), [Методы создания р-п переходов](#), [СБИС](#), [Технология КНИ](#), [Получение подложек для КНИ](#): Эпитаксиальный метод, Метод ионного внедрения, Метод сращивания пластин, Метод управляемого скола; [Литография в технологии КНИ](#); [Сверхтонкие проводники на платах](#); [Печатная электроника](#): глубокая печать, флексографская печать, офсетная печать, плоская трафаретная печать, ротационная трафаретная печать, струйная печать, лазерная аблация; [Органическая электроника](#); Источники электронов для вакуумных технологий.

### История микроэлектроники и начало наноэлектроники

Электроника прошла несколько этапов развития, за время которых сменилось несколько поколений элементной базы:

1. дискретная электроника электровакуумных приборов

2. дискретная электроника полупроводниковых приборов

3. интегральная электроника микросхем

4. интегральная электроника функциональных микроэлектронных устройств.

**Появлению электроники** предшествовало:

в 1809 году русский инженер Ладыгин изобрел лампу накаливания;

в 1874 году немецкий ученый Браун открыл выпрямительный эффект в контакте металл–полупроводник (диод);

в 1895 году русский изобретатель Попов изобрел радиоприемник;

затем были многочисленные разработки различных типов обнаружителей высокочастотных колебаний – детекторов, предвещающие возникновение электровакуумной электроники.

**К первому этапу** относятся:

в 1904 году английский ученый Флеминг создал электровакуумный диод;

в 1907 году была изобретена первая усилительная лампа – триод;

с неё и началось резкое развитие электронной техники;

в 1913 году немецкий инженер Мейснер разработал схему лампового регенеративного приемника и с помощью триода получил незатухающие гармонические колебания;

(в России первые радиолампы были изготовлены в 1914 году в Санкт-Петербурге консультантом русского общества беспроволочного телеграфирования Николаем Дмитриевичем Папалекси).

### **Второй этап** развития электроники:

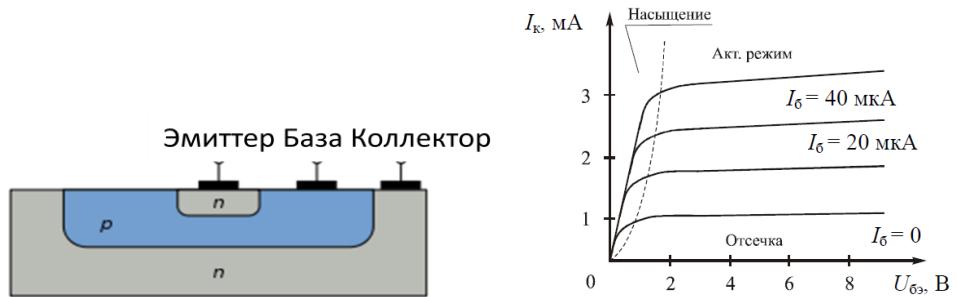

в 1946 году при лаборатории "Белл Телефон" была создана группа во главе с Уильямом Шокли, проводившая исследования свойств полупроводников на Кремнии и Германии. В итоге ею были изобретены: трехэлектродные полупроводниковые приборы – транзисторы. В зависимости от количества носителей заряда транзисторы были разделены на: униполярные (полевые), где использовались однополярные носители, и биполярные, где использовались разнополярные носители (электроны и дырки);

в 1953 году Дейки и Росс реализовали конструкцию полевого транзистора с управляющим p-n-переходом;

С появлением полевых и биполярных транзисторов начали воплощаться идеи разработки малогабаритных ЭВМ. Инженеры стали создавать бортовые электронные системы для авиационной и космической техники. Причём постоянно требовалось все большее и большее увеличение числа транзисторов в приборе, так что вскоре появились технические трудности, связанные с качеством монтажно-сборочных работ.

Решение проблемы межсоединений элементов электроники явилось предпосылкой к появлению микроэлектроники.

### **Третий этап** развития:

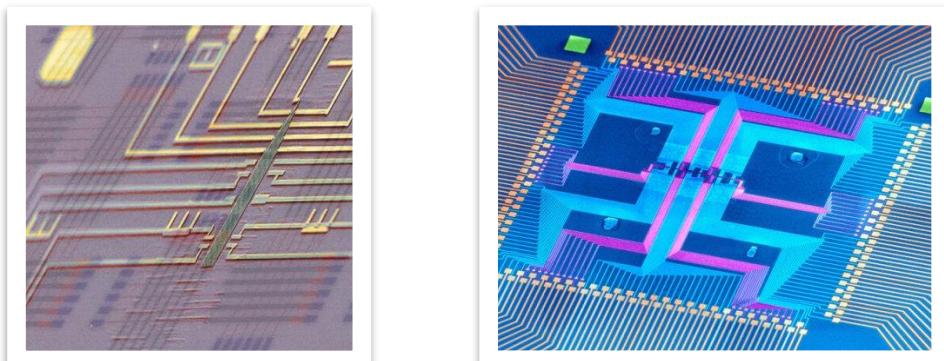

прообразом будущих микросхем послужила печатная плата, в которой все одиночные проводники были объединены в единое целое и изготавливались одновременно групповым методом (путем стравливания медной фольги с пластиной диэлектрика);

в 1960 году Роберт Нойс из фирмы Fairchild применил планарную технологию Хорни и изготовил первую кремниевую монолитную интегральную схему;

в том же году фирмой Fairchild было выпущено целое семейство монолитных транзисторно-транзисторных логических элементов с четырьмя и более биполярными транзисторами на одном кристалле кремния (появилось название "микрологика");

сначала интегральные микросхемы работали на биполярных транзисторах, а затем в 1965 году перешли на полевые;

в 1985 году появились КМОП (комплементарная структура металл-оксид-полупроводник, CMOS);

Технология “кремний на изоляторе” (КНИ) сделала создание полевых транзисторов доступным для производства в промышленных масштабах.

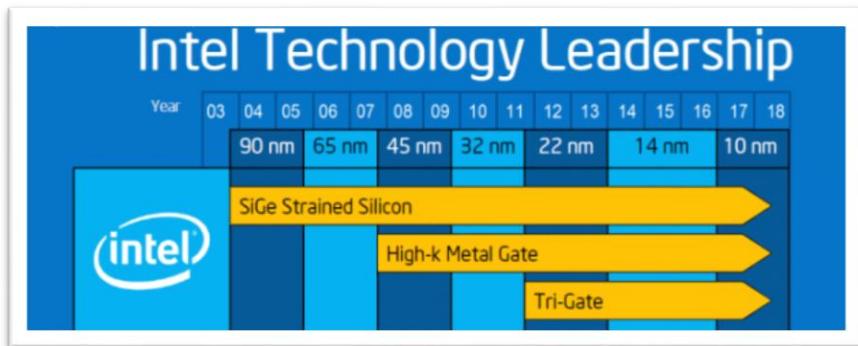

В 2012 году Intel начал выпуск процессоров с транзисторами на базе FinFET технологии (Tri-Gate транзисторы) с толщиной канала 22 нм.

В настоящее время микроэлектроника переходит на четвёртый уровень развития, превращается в наноэлектронику, которая базируется на фундаментальных исследованиях атомных процессов в полупроводниковых структурах пониженной размерности (квантовые точки, проволоки, ямы). Сегодня ведутся интенсивные научно-технические работы по поиску материалов и созданию из них элементов электроники нового поколения.

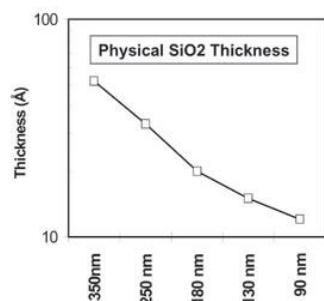

Развитие технологии полевого транзистора и сокращение толщины диоксида кремния:

| Кодовое обозначение процесса    | P856   | P858    | Px60             | P1262 | P1264 | P1266  | P1268 | P1270 |

|---------------------------------|--------|---------|------------------|-------|-------|--------|-------|-------|

| Год внедрения                   | 1997   | 1999    | 2001             | 2003  | 2005  | 2007   | 2009  | 2011  |

| Технологический процесс         | 250 нм | 180 нм  | 130 нм           | 90 нм | 65 нм | 45 нм  | 32 нм | 22 нм |

| Длина затвора                   | 200 нм | 130 нм  | 70 нм            | 50 нм | 35 нм | 25 нм  | 15 нм | 9 нм  |

| Материал межслойного соединения | Al     |         |                  | Cu    |       |        |       | Н/д   |

| Дизэлектрик затвора             |        |         | SiO <sub>2</sub> |       |       | high-K |       |       |

| Материал затвора                |        |         | Поликремний      |       |       | Металл |       |       |

| Размер подложки (wafer), мм     | 200    | 200/300 |                  |       | 300   |        |       |       |

Инженеры из Гарварда и компании MITRE Corporation создали первый в мире программируемый нанопроцессор. Удалось создать стандартные вычислительные блоки, соединив их с помощью нанопроводников в единую сложную схему нанопроцессора.

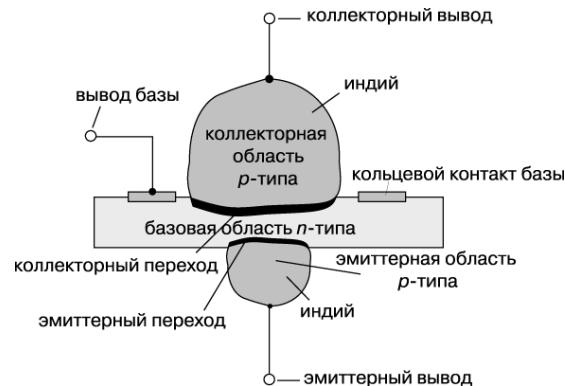

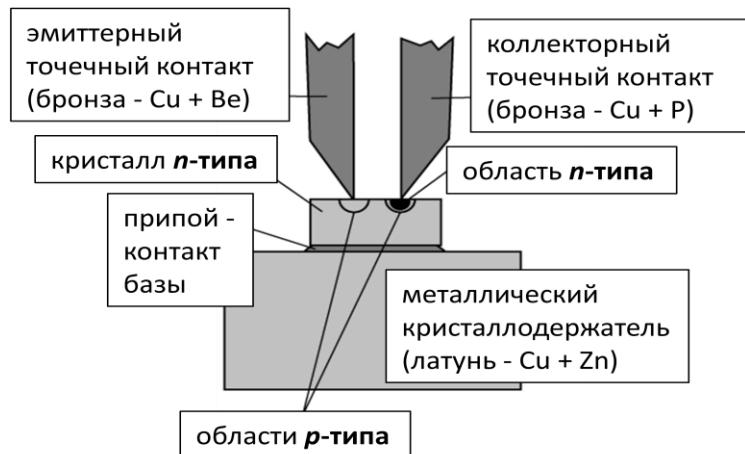

## Биполярный транзистор

### Примеры "допотопного изготовления"

#### Сплавной плоскостной транзистор

#### Точечный транзистор

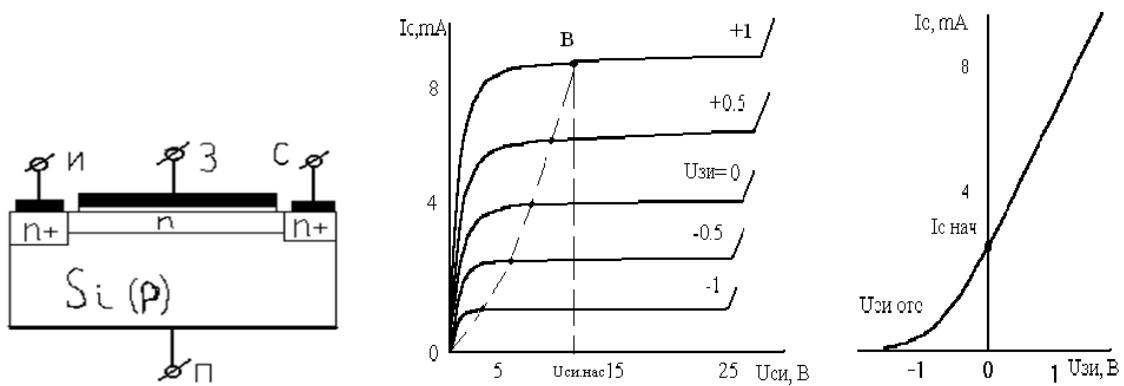

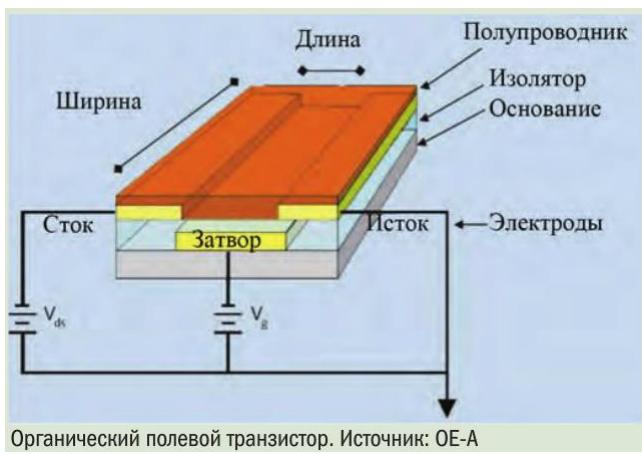

## Полевой транзистор

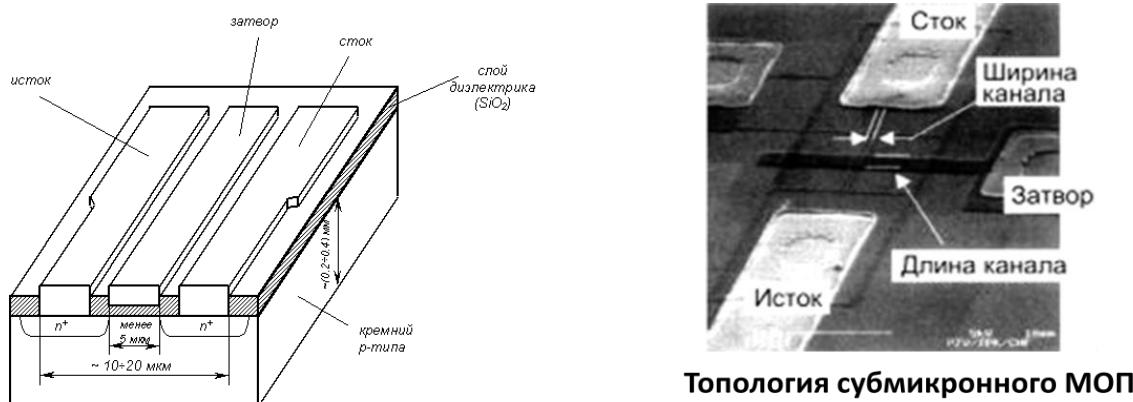

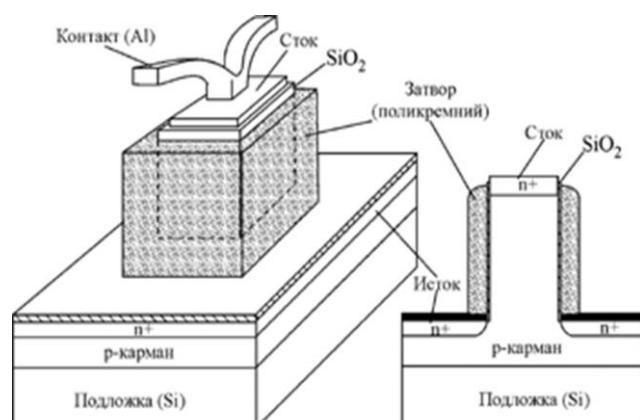

Структура n-канального МОП транзистора:

Топология субмикронного МОП

Изготовление МОП много проще, чем биполярных, к тому же МОП могут использоваться как резисторы и конденсаторы, т.е. на них можно реализовать все схемные функции.

МОП:

$$I_{\text{bx}} = 5 \text{ мА}, R_{\text{bx}} = 106 \text{ Ом}, R_{\text{i-c закр.}} = 1012 \text{ Ом}, R_{\text{i-c откр.}} \sim 100 \text{ Ом}, C_{\text{i-c}} = 10 \text{ пФ}.$$

Бип. :

$$I_{\text{bx}} = 1 \text{ мА}, R_{\text{bx}} \sim 100 \text{ Ом}, R_{\text{i-c закр.}} \sim 100 \text{ Ом}, R_{\text{i-c откр.}} \sim 10 \text{ Ом}, C_{\text{i-c}} = 10 \text{ пФ}.$$

## Примеры промышленных МОП транзисторов

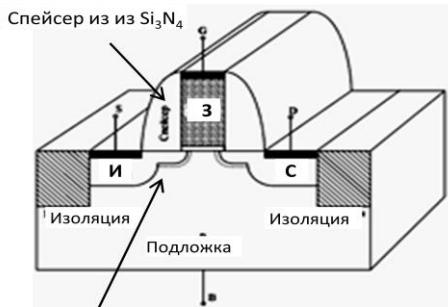

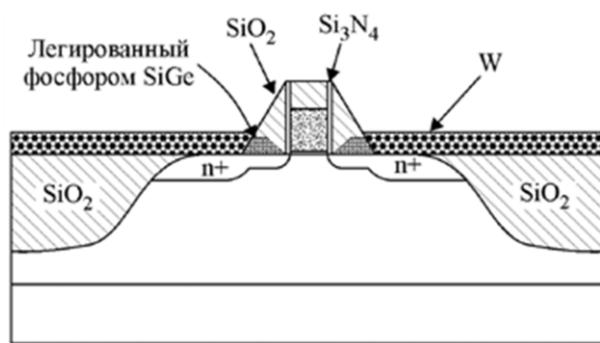

**LDD структура (Lightly Doped Drain):** структуры с дополнительными слаболегированными областями.

Слаболегированные области с плавным р-п переходом удлиняют И и С в сторону канала, повышая  $U_{\text{пробоя}}$ .

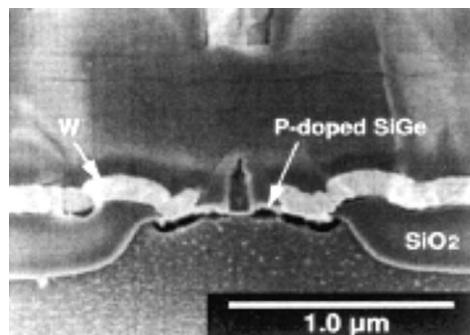

Мелкие области истока и стока получены диффузией из легированного фосфором  $\text{SiGe}$

**КНИ-структура (кремний-на-изоляторе)**

**Фотография МОП**

Кармашки, легированные бором для n-канальных МОП (p-карман) и фосфором для p-канальных (n-карман), нужны для предохранения от смыкания истока и стока, а также подавления эффекта снижения порогового  $U$  с уменьшением длины канала.

**"Кремний ни на чём"**

**Цилиндрический канал**

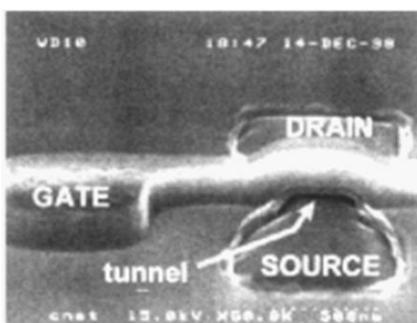

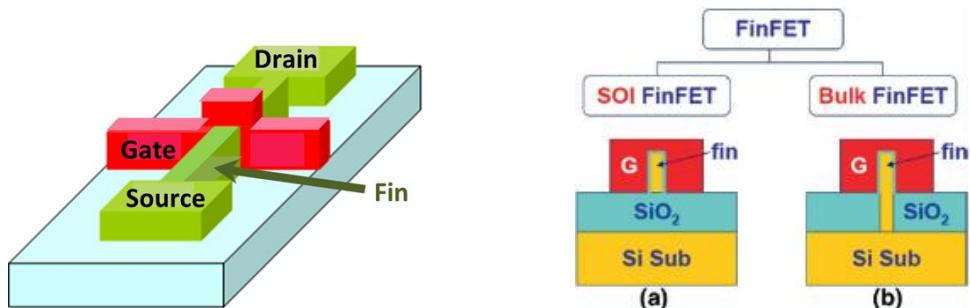

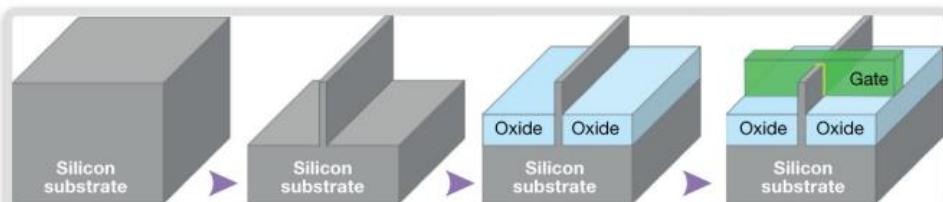

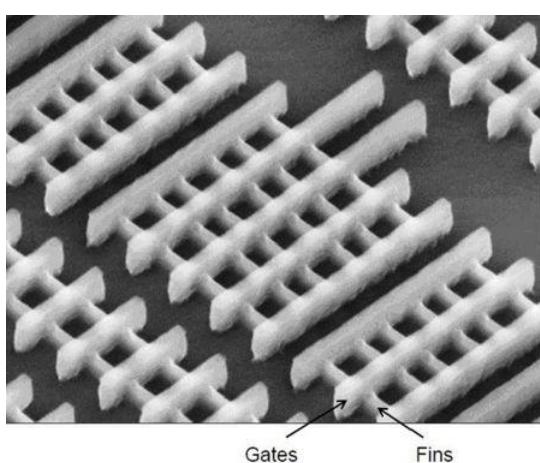

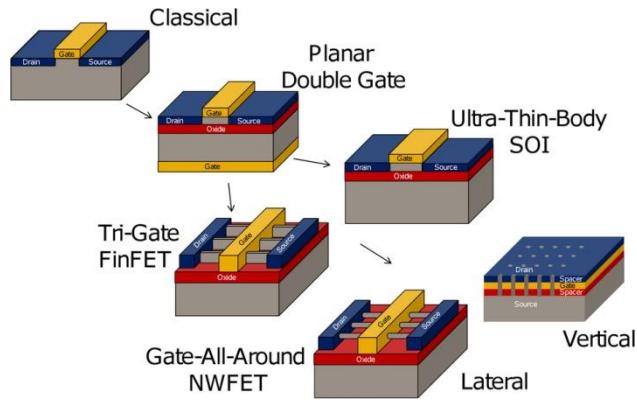

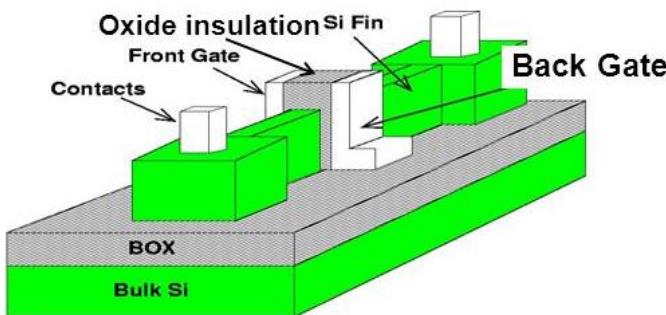

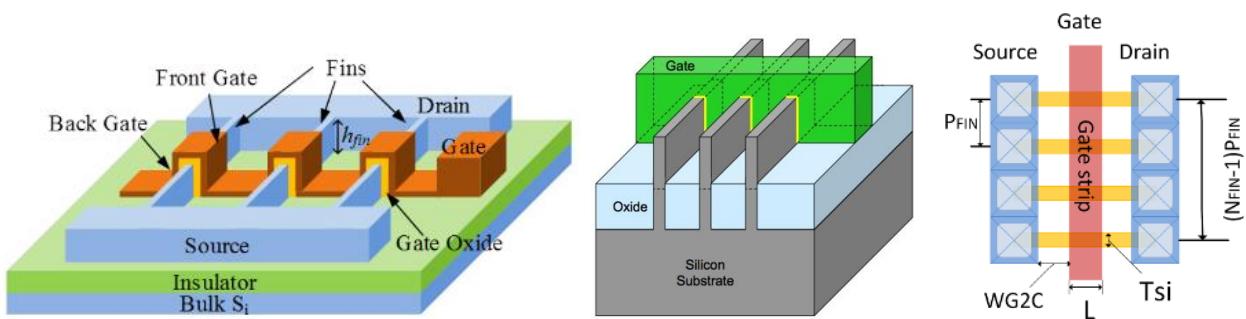

## FinFET транзисторы

**FinFET транзисторы** - это направление в проектировании микросхем, в котором за счет использования трехмерного затвора транзистора в форме плавника повышается эффективная ширина затвора (при той же площади логической ячейки, что и с плоским затвором). Основу структуры составляет “плавник” (fin) - область диффузии для стока и истока, которая окружена затвором.

Два варианта литографического создания FinFET транзистора для SOI и Bulk:

(a) Normal Wafer: FinFETs on regular wafers rely on a timed etch to form the fins

(b) Silicon-on-Insulator Wafer: FinFETs on SOI wafers rely on the buried oxide layer to stop the fin etch

Результат перехода на FinFET транзисторы: снижение сопротивления транзистора в открытом состоянии, увеличение сопротивления в закрытом состоянии, более быстрое переключение между этими состояниями, снижение рабочего напряжения и уменьшение токов утечки, новый уровень энергоэффективности, прирост производительности.

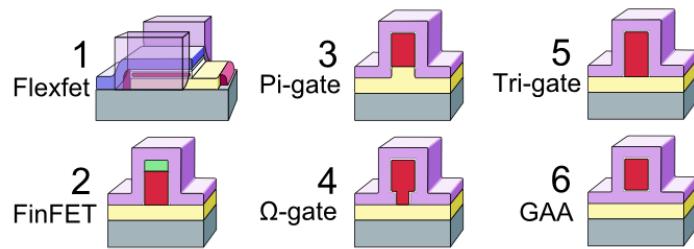

### Разновидности FinFet

Independent-Gate (IG FinFET) - затворы транзистора независимы (на каждый затвор подается свой сигнал). Интересны с точки зрения применения для создания простейших логических топологических единиц.

Tri-gate (TG FinFET) - затворы транзистора соединены между собой. В данный момент активно осваивается в приложении к высокопроизводительным системам.

Вариантов взаимного расположения и формы затвора, эмиттера и коллектора очень много.

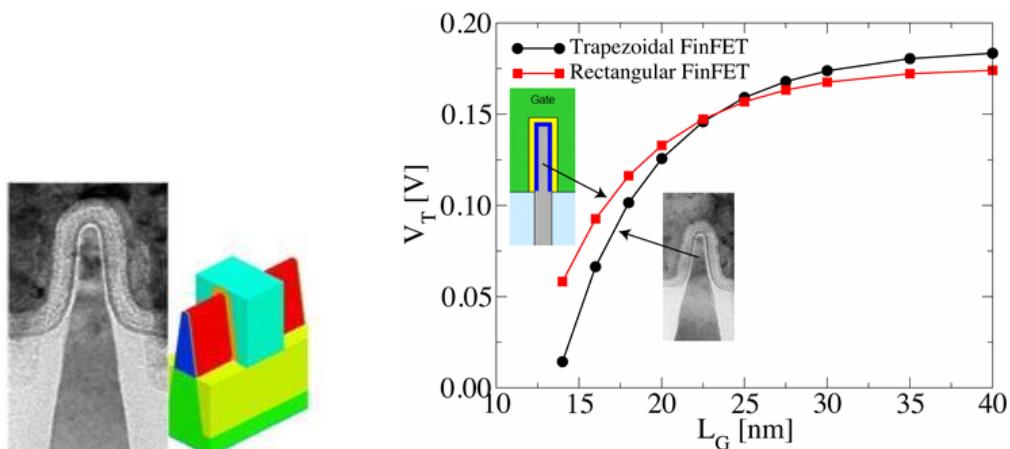

В данный момент идут интенсивное изменение и поиск оптимальной геометрической формы плавника. Известно, что треугольная форма транзисторов обеспечивает больший выход годных и надежность. При этом облегчается вертикальное протравливание транзисторной структуры и достигается более надежное осаждение диэлектрической пленки.

Зависимость порогового напряжения от длины затвора двух форм: трапециевидной и идеальной прямоугольной.

Вертикальное расположение даёт возможность изменить длину соединений и соответственно шумов и паразитных излучений. А также длину пути сигнала, что способствует улучшению частотных характеристик. Но за все приходится платить - в данном случае сильно возросшим тепловым потоком.

## **Методы создания р-п переходов**

### **1. Метод вытягивания:**

в процессе вытягивания п/п монокристалла из расплава в него вводят сначала примесь n-типа, а затем p-типа

### **2. Диффузионный метод:**

диффузия акцепторной примеси в донорный полупроводник.

### **3. Эпитаксиальный метод:**

осаждение на n-Si монокристаллической плёнки p-Si

### **4. Метод ионного легирования:**

поверхностный слой полупроводника n-типа легируется ионным пучком примесью p-типа

### **5. Метод печати**

## Интегральные схемы

**Пленочная интегральная схема** — это микросхема, чьи элементы выполнены в виде пленок, нанесенных на поверхность диэлектрической подложки (стекло, керамика и др.). В зависимости от толщины пленок различают тонко пленочные (1-2 мкм) и толстопленочные (10-20 мкм и выше) интегральные схемы. В толстопленочных технологиях используются пасты различного состава, в тонкопленочных технологиях пленки осаждаются на подложку из газовой фазы. Пленочные микросхемы содержат только пассивные элементы (резисторы, конденсаторы и т. д.), поскольку получить в пленках активные компоненты (транзисторы) пока еще не удалось. Как следствие, такие микросхемы функционально очень ограничены.

**Полупроводниковая интегральная схема** — это микросхема, элементы которой выполнены в приповерхностном слое полупроводниковой подложки. Технология их изготовления основана на легировании полупроводниковой (кремниевой) пластины поочередно донорными и акцепторными примесями, в результате чего под поверхностью образуются тонкие слои с разным типом проводимости и p-n-переходы. При этом отдельные слои используются в качестве резисторов, а p-n-переходы предназначены для реализации диодов и транзисторов.

Локальное легирование осуществляется с помощью масок, причем роль маски обычно выполняет пленка двуокиси кремния ( $\text{SiO}_2$ ), покрывающая поверхность кремниевой пластины. "Окна" в этой пленке гравируются специальными методами. Фрагмент структуры полупроводниковой интегральной схемы:

В электрических схемах, реализованных на базе дискретных радиоэлементов, разработчики обычно отдают предпочтение пассивным радиоэлементам. Активные радиоэлементы, особенно транзисторы, намного дороже. Поэтому оптимизация электрической схемы сводится к уменьшению их числа.

Однако в микроэлектронике главенствующее положение занимает не стоимость отдельных радиоэлементов, а стоимость совокупности таких радиоэлементов (интегральной

схемы в целом). С этой точки зрения желательно разместить в кристалле как можно больше радиоэлементов. Можно разместить максимальное количество тех элементов, у которых меньшая площадь. А такую площадь имеют активные радиоэлементы. Поэтому схемотехнические решения на интегральных схемах выполняются по принципу "сделать наоборот". Предпочтение отдается активным радиоэлементам (транзисторам, диодам), а количество пассивных радиоэлементов (резисторов и конденсаторов) сводится к минимуму.

## Создание СБИС

Большие и сверхбольшие интегральные микросхемы (СБИС) на современном уровне представляют последний этап развития классических интегральных микросхем (классические - в которых можно выделить области, эквивалентные пассивным и активным элементам).

В настоящее время применяют групповые способы изготовления полупроводниковых интегральных микросхем, позволяющие за один технологический цикл получить несколько сотен заготовок микросхем. Наибольшее распространение получил групповой планарный способ, заключающийся в том, что элементы микросхем (конденсаторы, резисторы, диоды и транзисторы) располагаются в одной плоскости или на одной стороне подложки.

Технология получения полупроводниковых интегральных схем состоит из 15—20, а иногда и более операций.

Самым распространенным методом получения элементов в микросхеме является изоляция их друг от друга оксидной пленкой, которая возникает на проводящей подложке в результате её термообработки.

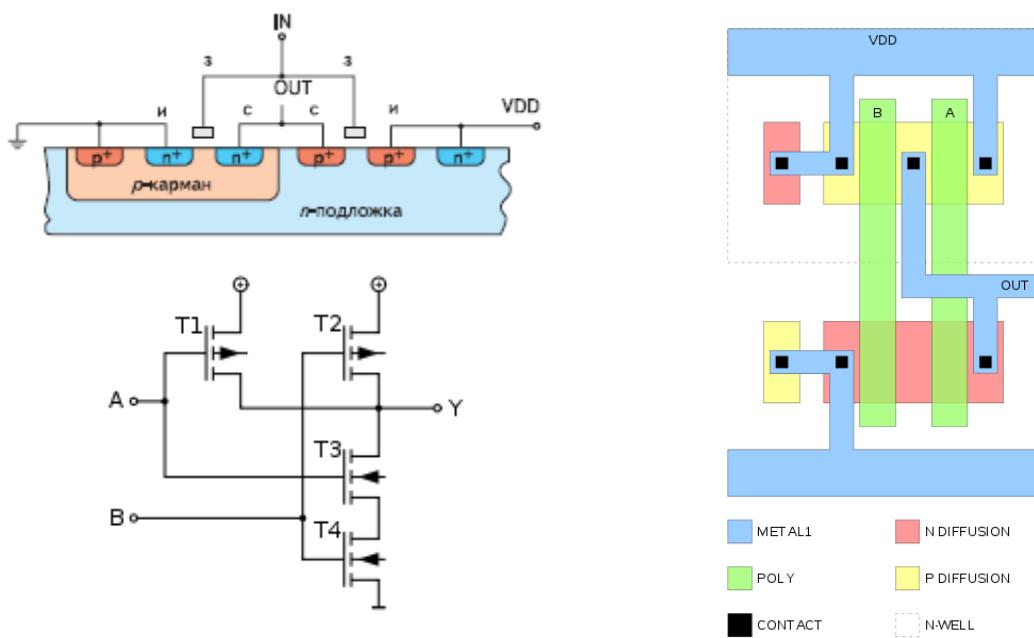

На рисунке представлена топология логического элемента 2И-НЕ (технология КМОП).

## Изоляция слоёв

**Термическое окисление кремния** — одна из основных операций изготовления полупроводниковых микросхем: проводится при температуре чуть выше 1000С в атмосфере кислорода (сухое окисление) или в смеси кислорода с парами воды (влажное окисление). Причем толщина диэлектрического покрытия увеличивается до ~0,1 мкм.

В **алио-мооксидной технологии** изоляцию между соседними проводниками осуществляют слои пористого Al2O3.

Какие другие материалы могут создавать изоляцию? **Полимеры**. Но большинство полимеров недостаточно термостойки и поэтому не могут быть использованы в технологии изготовления микросхем. Правда, есть одно исключение — фторсодержащие полимеры.

**Изоляция р-п-переходом** сводится к реализации между изолируемыми элементами двух встречновключённых диодов. Обедненный слой р-п-перехода, особенно при большом обратном смещении, имеет очень высокое удельное сопротивление, близкое к удельному сопротивлению диэлектрика. Изоляция р-п-переходом очень хорошо вписывается в общий технологический цикл изготовления биполярных схем.

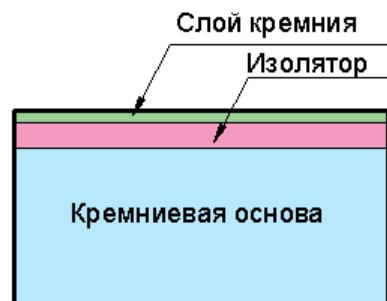

### Технология КНИ

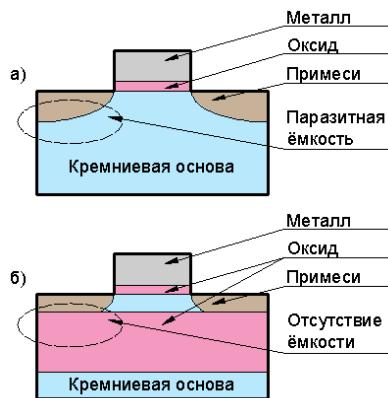

Кремний на изоляторе (КНИ, англ. Silicon on insulator, SOI) — технология изготовления полупроводниковых приборов, основанная на использовании трёхслойной подложки со структурой кремний-диэлектрик-кремний вместо обычно применяемых монолитных кремниевых пластин. Максимальная частота переключения транзисторов (Ft), выполненных по технологическому процессу 130 нм, может достигать 200 ГГц.

Основное преимущество технологии КНИ состоит в том, что за счёт тонкости поверхностного слоя и изоляции транзистора от кремниевого основания удаётся многократно снизить паразитную ёмкость, а значит и снизить время её зарядки вкупе с потребляемой мощностью.

В настоящее время наиболее распространены КНИ-подложки, где в качестве изолятора выступает диоксид кремния ( $\text{SiO}_2$ ).

## **Получение подложек для КНИ**

Подложки могут быть получены различными способами. Самые распространённые: эпитаксия, ионное внедрение, срашивание пластин, управляемый скол.

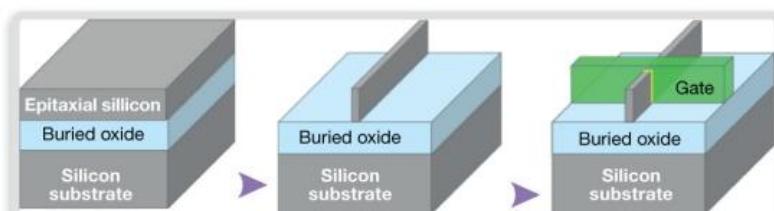

### **1. Эпитаксиальный метод (или seed method)**

В случае использования эпитаксиальной технологии поверхностный слой образуется за счёт выращивания кремниевой плёнки на поверхности диэлектрика.

Активные элементы, полученные на таких подложках, демонстрируют отличные рабочие характеристики, но большое число технологических проблем, связанных с эпитаксиальным процессом, пока ещё не дают возможностей для массового внедрения этой технологии.

### **2. Метод ионного внедрения (или ионная имплантация или имплантация кислорода SIMOX - Separation by IMplantation of OXygen или ионный синтез захороненных диэлектрических слоев).**

При использовании данной технологии монолитная кремниевая пластина подвергается интенсивному насыщению кислородом путём бомбардировки поверхности пластины его ионами с последующим отжигом при высокой температуре, в результате чего образуется тонкий поверхностный слой кремния на слое оксида.

При производстве таких подложек приходится использовать сложные сильноточные ускорители ионов кислорода. Это обуславливает их высокую цену. А большая плотность дефектов в рабочих слоях является серьёзным препятствием при массовом производстве полупроводниковых приборов.

### **3. Метод срашивания пластин (или wafer bonding)**

При использовании технологии срашивания пластин образование поверхностного слоя производится путём прямого срашивания второй кремниевой пластины со слоем диоксида. Для этого гладкие, очищенные и активированные за счёт химической или плазменной обработки пластины подвергают сжатию и отжигу, в результате чего на границе пластин происходят химические реакции, обеспечивающие их соединение.

Данная технология практически идеальна для изготовления КНИ-подложек с толстым поверхностным слоем. Но с уменьшением толщины слоя (менее 1 мкм) в нём начинает нарастать плотность дефектов. Кроме того, усложняется технологический процесс и растёт стоимость изделий, что делает процесс ничем не лучше ионного внедрения.

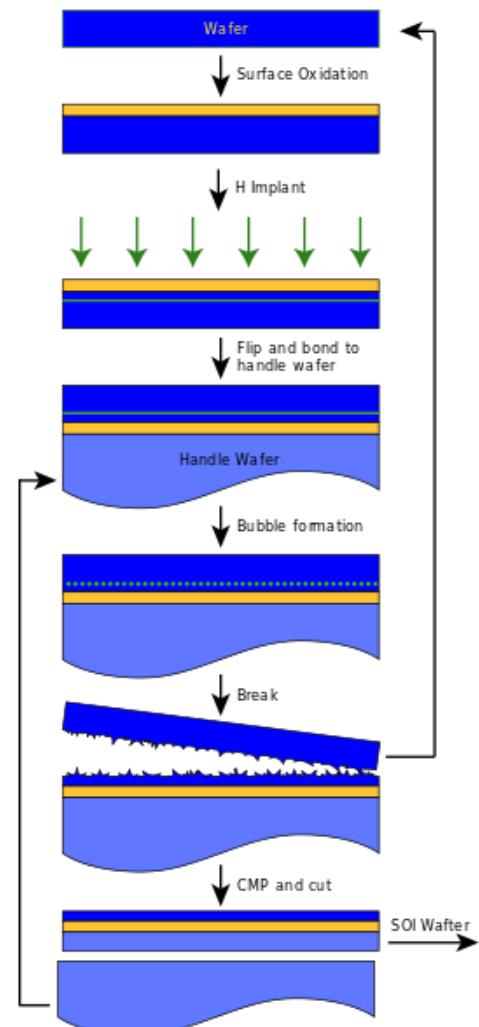

#### 4. Метод управляемого скола (или Smart Cut)

Технология управляемого скола, разработанная французской компанией Soitec, объединяет в себе технологии ионного внедрения и срашивания пластин.

В технологическом процессе используются две монолитные кремниевые пластины. Первая пластина подвергается термическому окислению, в результате чего на её поверхности образуется **слой диоксида** (на рис справа жёлтый), затем верхняя лицевая поверхность подвергается насыщению ионами водорода с использованием технологии ионного внедрения. За счёт этого в пластине создаётся область скола (за диоксидом), по границе которой пройдёт отделение оставшейся массы кремния. По завершении процедуры ионного внедрения пластина переворачивается и накладывается лицевой стороной на вторую пластину, после чего происходит их срашивание (пунктиру на рис справа). На завершающей стадии проводится механическое отделение первой пластины, в результате которого на поверхности второй остаётся слой диоксида и тонкий поверхностный слой кремния. Отделённая часть первой пластины не выбрасывается, а используется в новом производственном цикле.

Производство КНИ-подложек по технологии управляемого скола требует большого количества операций, но в его процессе используется только стандартное оборудование.

Важным достоинством пластин, полученных по этой технологии, является низкая плотность дефектов в рабочем слое.

## Литография в технологии КНИ

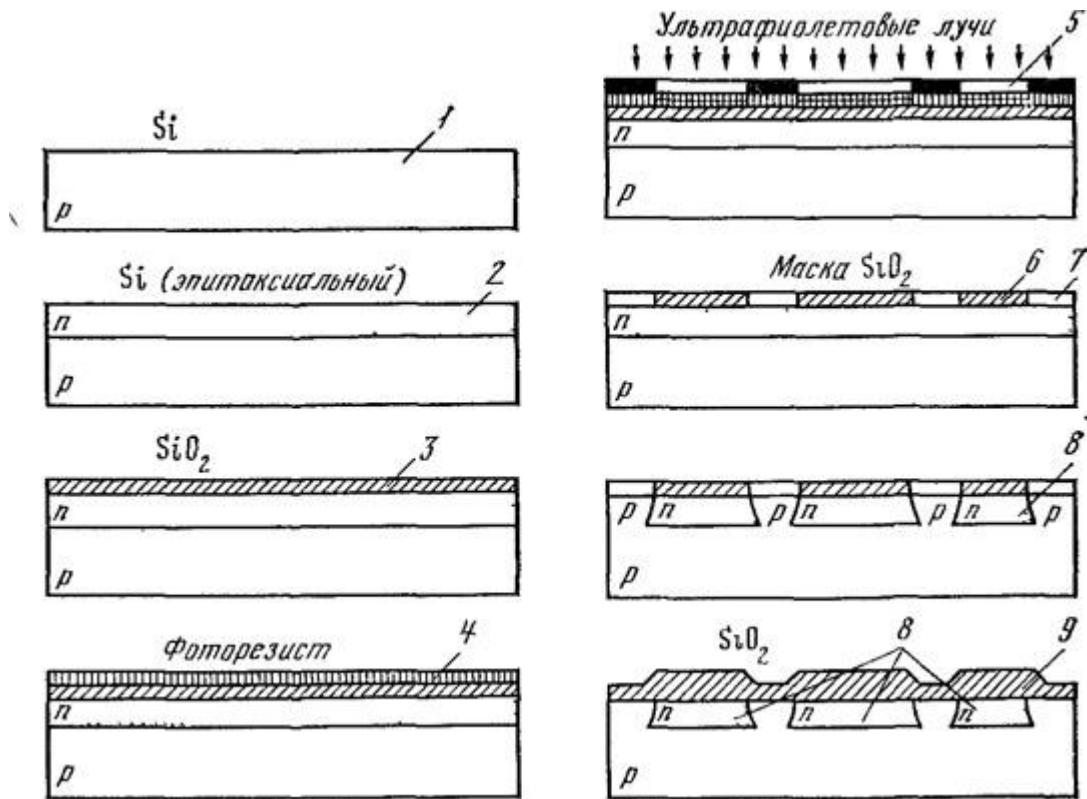

Получение внутрисхемных соединений с помощью фотолитографии.

Пример литографической обработки с УФ облучением

- 1 – подложка

- 2 – поверхностный слой кремния

- 3 - оксидная пленка

- 4 – фоторезист

- 5 – фотошаблон

- 6 – поверхность оксида кремния

- 7 – нерастворенные участки

- 8 – изолирующий барьер

- 9 - активные и пассивные элементы

- схемы и токопроводящие пленки

## Электрические контакты

После того как получены все компоненты схем и пленка оксида вытравлена с тех мест, где будут находиться выводы компонентов, полупроводниковую схему покрывают методом напыления или гальванического осаждения пленкой алюминия (основной материал, используемый для металлизации). Удельное сопротивление алюминия меньше, чем у меди, но он обладает прекрасной адгезией к оксиду кремния, хорошо сваривается с тем же алюминием или золотом (внешние выводы).

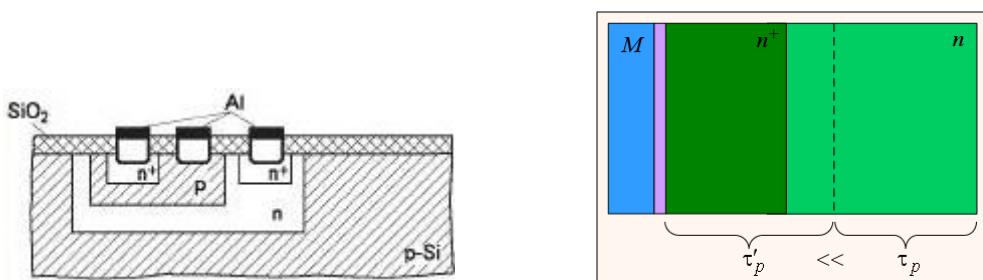

По ряду причин пленку первичного алюминия нельзя просто напылить на поверхность кремния (отслаивается при перепаде температур). Поверхностный слой кремния легируется алюминием, который по отношению к кремнию является акцептором. Как следствие, атомы алюминия в приповерхностном слое создают р-слой. Как предотвратить образование ненужных р-п-переходов в таких слоях? Создаётся **омический переход**.

Основное назначение омических переходов – качественное электрическое соединение полупроводников с металлическими токоведущими частями прибора. Эту задачу решают с помощью типового приема "**предварительно напряженное действие**". Суть приема в следующем: объекту заранее придается изменение, противоположное нежелательным рабочим изменениям. Чтобы избежать образования приповерхностного р-слоя, область п-слоя вблизи контакта дополнительно легируют донорными примесями, превращая ее в п+-слой. Концентрации алюминия становится недостаточно для образования р-слоя, и р-п-переход не образуется.

Омический переход имеет наименьшее отрицательное влияние на характеристики прибора, если выполняются условия:

- ВАХ омического перехода линейна

(т.е. ток растёт с ростом напряжения без отклонений от прямой)

- на омическом переходе реализуется минимально возможное падение напряжения  $U$

(т.е. у него минимальное сопротивление)

- отсутствует инжекция неосновных носителей заряда через омический переход, а также накопление неосновных носителей вблизи перехода. Для этого металл и полупроводник подбирают с равной или близкой работой выхода, выравнивая потоки электронов вдоль уровня Ферми, или сильно легируют поверхность полупроводника, приближая его к металлу по концентрации электронов (область  $n^+$  на диаграмме).

Структура реального омического контакта в полупроводниковых приборах имеет сложное строение и состоит из нескольких омических переходов.

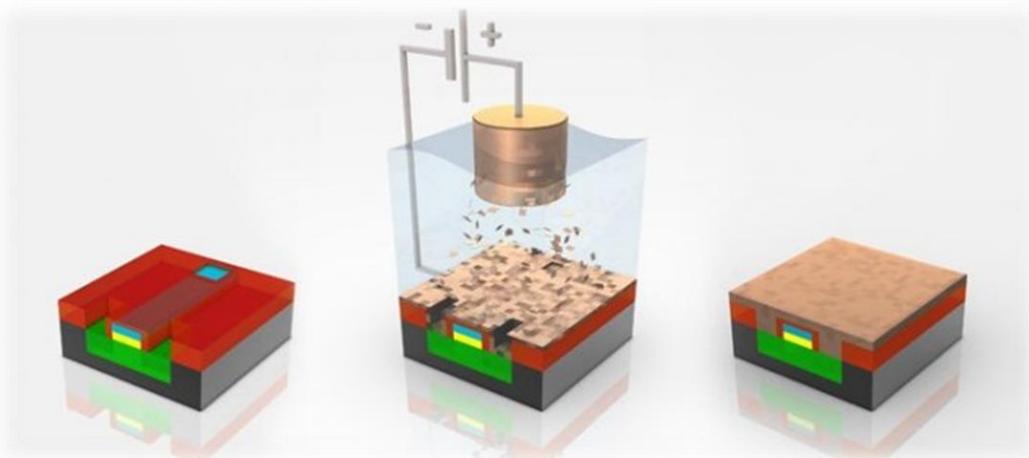

### Электролитические контакты

Для электрического соединения логических элементов, пластины помещают в раствор сульфата меди, в котором под действием электрического тока атомы металла «оседают» в оставшихся «проходах».

В гибридных интегральных схемах в качестве навесных радиоэлементов применяются бескорпусные диоды, транзисторы и бескорпусные интегральные схемы. Традиционный вариант установки таких радиоэлементов на материнскую интегральную схему предусматривает использование проволочных выводов радиоэлементов. После фиксации радиоэлементов эти выводы соединяются с контактными площадками, чаще всего — методом компрессионной термосварки.

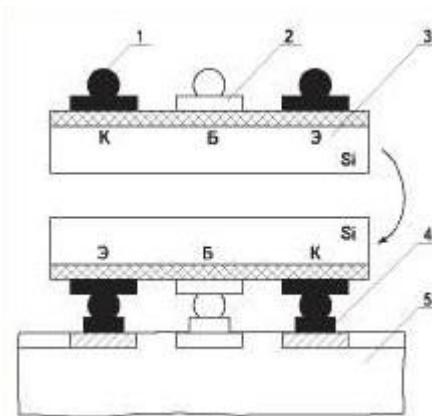

Проволочные выводы выходят за границы кристалла, увеличивая его реальную площадь. Однако же в идеале реальная площадь не должна выходить за пределы, ограниченные периметром кристалла! Сделать это удалось, перевернув кристалл вверх ногами. Выводы таких радиоэлементов выполняются в виде шариков. Для обеспечения прочного соединения используется термокомпрессия. Метод перевернутого монтажа (flip-chip) позволяет существенно сэкономить площадь подложки гибридной интегральной схемы.

Монтаж бескорпусного транзистора с шариковыми выводами: 1 — шарики, 2 — контактные площадки транзистора, 3 — транзистор, 4 — контактные столбики подложки, 5 — подложка.

Тот же метод активно применяется и в надсистеме. Для интегральных схем надсистема — печатная плата. Использование микросхем с матричными выводами — одно из основных направлений увеличения плотности межсоединений в печатных узлах.

Новое технологическое поколение упаковки чипов — **System-in-Package** (SIP). Решения на основе SIP-технологий находит широкое применение в различных сегментах рынка, в частности, в бытовой электронике (цифровые камеры и видеокамеры, автомобильная электроника, медицина, средства телекоммуникации, военная и авиационно-космическая техника). Конструктивные решения многокристальных модулей, созданные по этой технологии, разнообразны. Представьте себе, что на рисунке выше изображен не транзистор, а микромодуль. Если на этот микромодуль установить еще один микромодуль, а на него еще один и т. д., то получится многокристальный модуль в виде своеобразной этажерки микромодулей (Stacked Package).

## Борьба с паразитной ёмкостью

При построении схемы по технологии CMOS большая часть потребляемой мощности затрачивается на заряд паразитной ёмкости изолирующего перехода (в момент переключения транзистора из одного состояния в другое), а время, в течение которого формируется этот заряд, определяет общее быстродействие схемы.

## Печатная электроника

Печатная электроника – область электроники, занимающаяся созданием электронных схем с помощью печатного оборудования, которое позволяет наносить на поверхность плоской подложки специальные краски (токопроводящие, полупроводниковые, резистивные и т.д.) и, таким образом, формировать на ней активные и пассивные элементы, а также межэлементные соединения в соответствии с электрической схемой.

При печати может использоваться оборудование для трафаретной печати, флексографии, ротогравюрной и офсетной печати, а также струйные принтеры.

Могут использоваться любые материалы: органические полупроводники, неорганические полупроводники, металлические проводники, наночастицы, углеродные нанотрубки и т.д.

Наиболее применяемые в печатной электронике материалы:

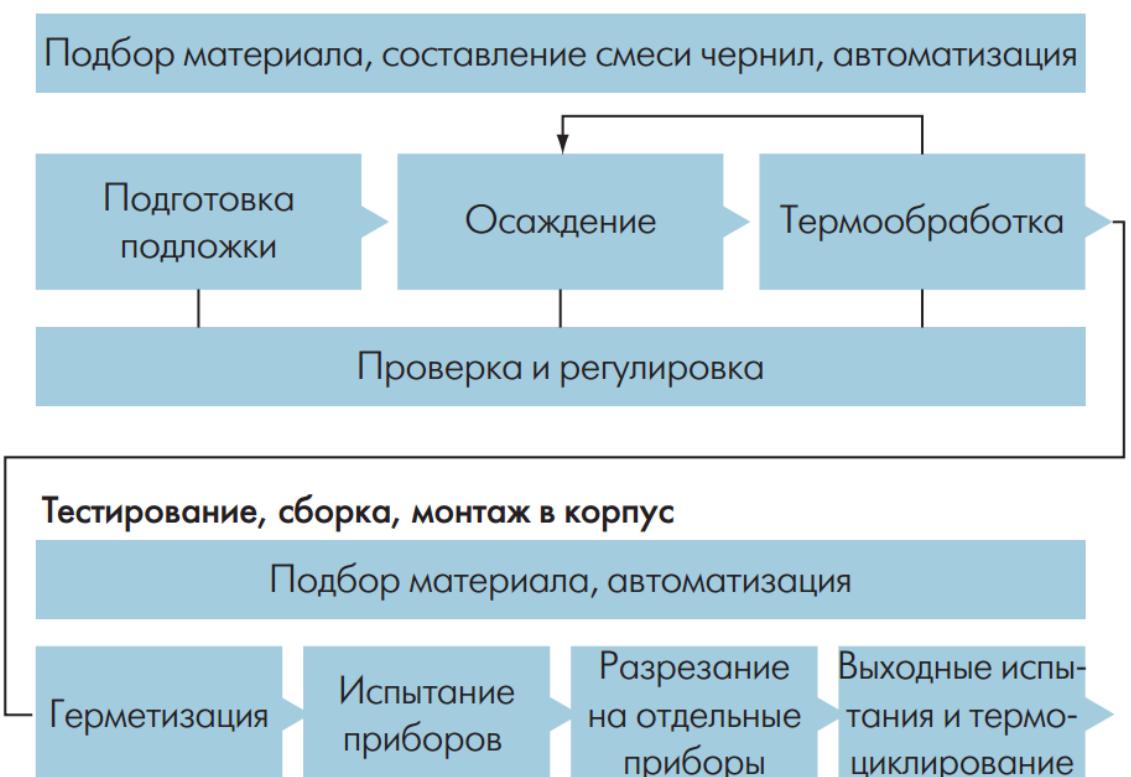

## Процесс производства печатной полупроводниковой схемы

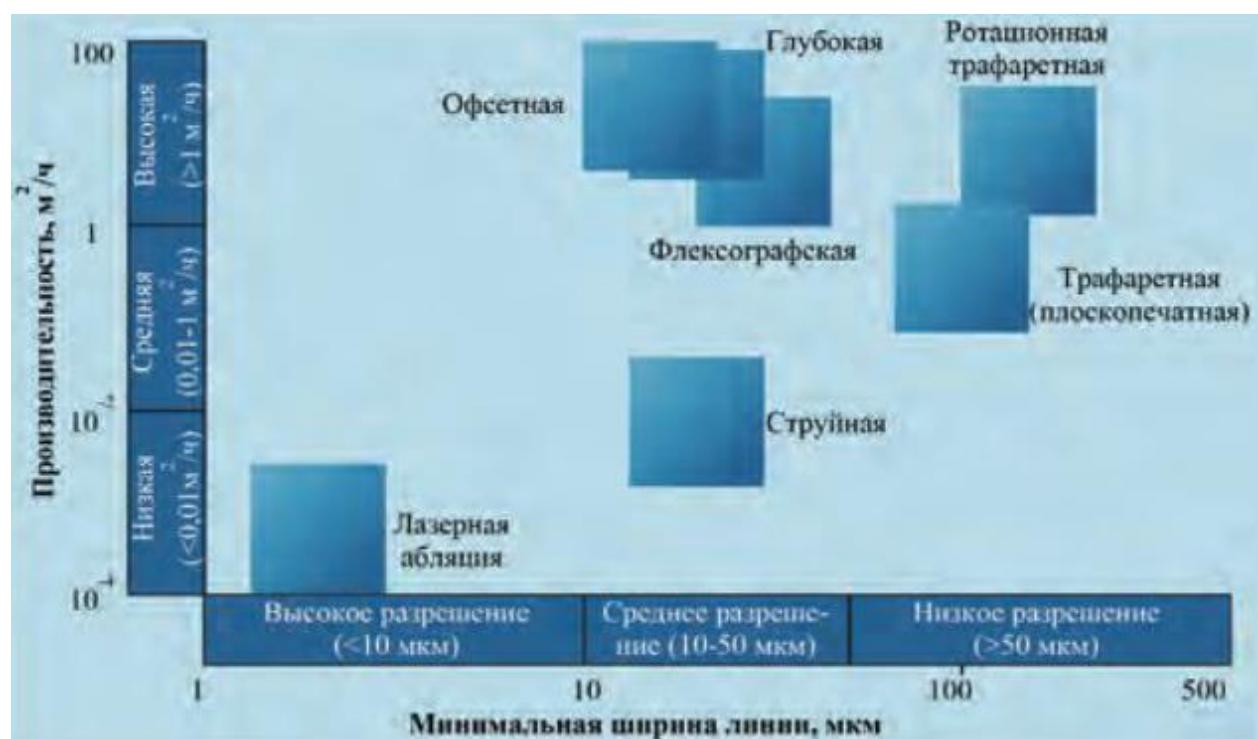

Производительность и минимальная ширина линии основных технологий печати

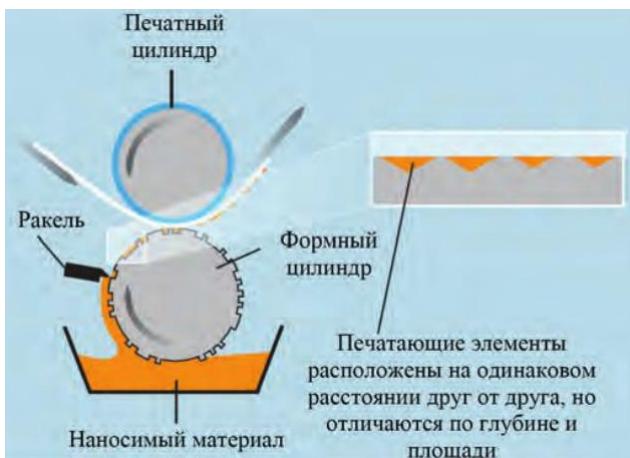

## 1. Глубокая печать

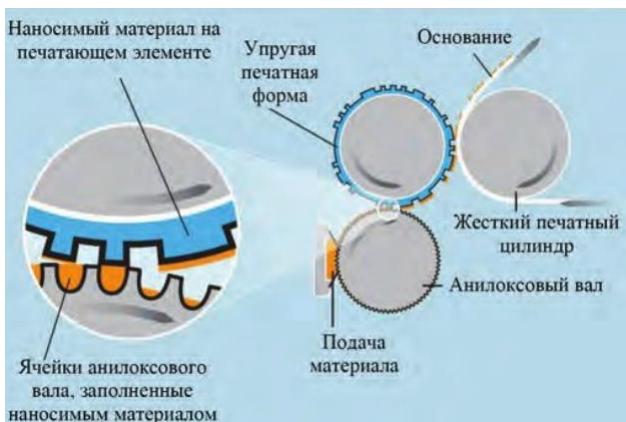

## 2. Флексографская печать

## 3. Офсетная печать

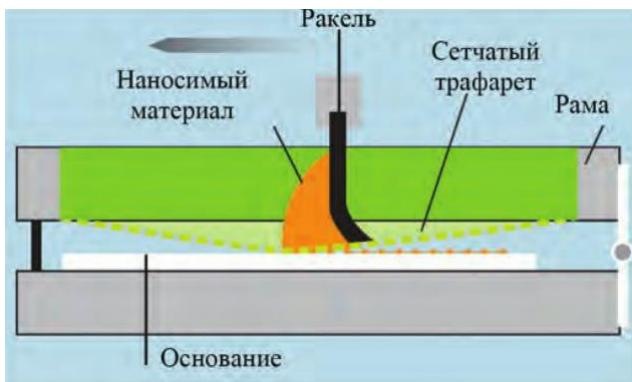

#### 4. Плоская трафаретная печать

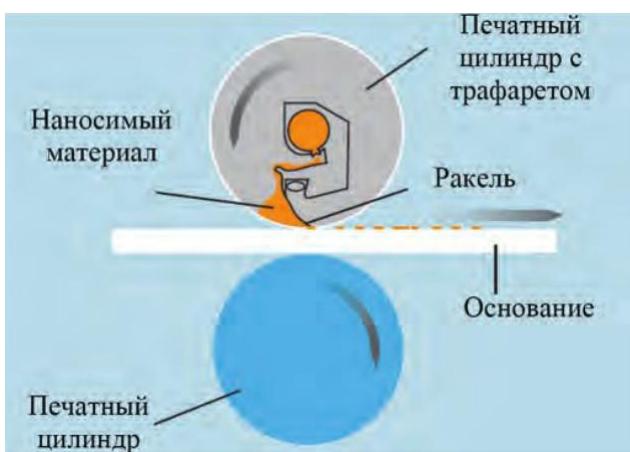

#### 5. Ротационная трафаретная печать

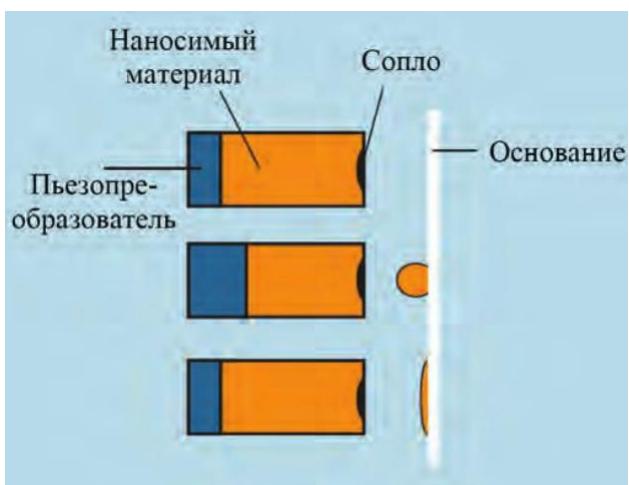

#### 6. Струйная печать

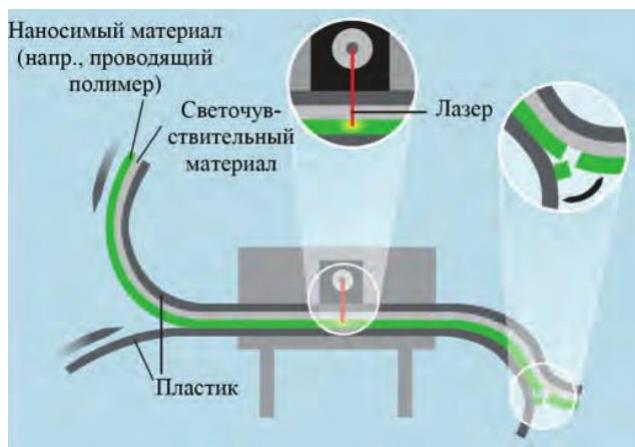

## 7. Лазерная аблация

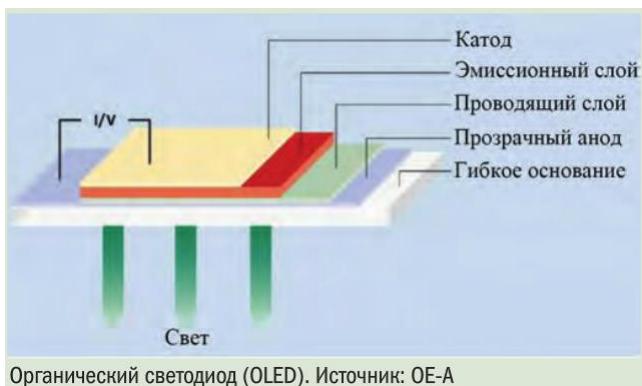

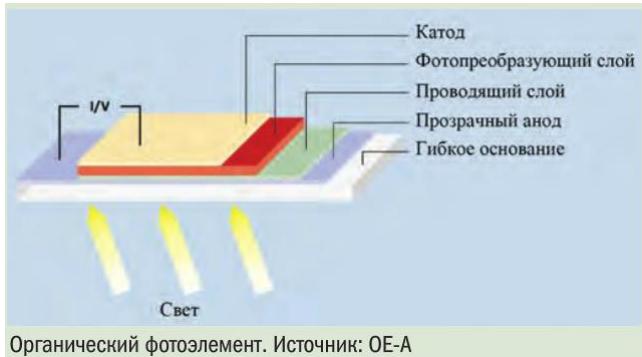

## Органическая электроника

## **Заключение**

В ближайшие 10-20 лет, скорее всего, изменится материальная часть наноэлектроники ввиду того, что технологический процесс достигнет физических пределов производства. Возможно, это будут:

Оптические компьютеры — в которых вместо электрических сигналов обработке подвергаются потоки света (фотоны, а не электроны).

Квантовые компьютеры, работа которых всецело базируется на квантовых эффектах. В настоящее время ведутся работы над созданием рабочих версий квантовых процессоров.

Молекулярные компьютеры — вычислительные системы, использующие вычислительные возможности молекул (преимущественно, органических).

## **Басня:**

Бог слепил человека из глины, и остался у него неиспользованный кусок.

- Что еще слепить тебе? - спросил Бог.

- Слепи мне Счастье, - попросил человек.

Ничего не ответил Бог, и только положил человеку в ладонь оставшийся кусочек глины.